| 1 |

Subject: University-Industry Link Campus Open Day, Sungai Long

Following the open day on 23 July 2016 in Sungai Long and meeting with Mr. Wong Chong Wai, a member of staff of the Devices and Develop Group of Intel, an UTAR-Intel collaboration Lab Project meeting was held at the invitation of Intel on 18 October 2016. Intel proposed to help UTAR with lab practices for VLSI related subjects. The collaboration agenda was minute.

In a meeting on 1 November 2016, Intel presented the lab practical/projects proposal.

- Speech Recognition System

- Image Tile Compression Engine

- Intelligent Traffic Light Controller

- Projects will make use of Verilog, Synopsys and Intel FPGA

The proposed lab assignment on the Traffic Light Controller reused the same template as the lab assignment (ALU) from UTAR.

In summary

- Assignment #1: Start off with controlling a simple traffic light, then move on to design a cross-junction Traffic Light Controller

- Assignment #2: Complete the design of an intelligent Traffic Light Controller by adding intelligence (based on sensors input) to the base design in Assignment #1

- Assignment #3 (IC compiler) is changed to be based on the Traffic Light Controller above.

As discussed, students have opportunity to implement this design using FPGA. Several meetings were held in 2017 and 2018 to sort out problems and to work out solutions.

A meeting was held on 5 December 2018 to conduct a review session about progress update. Progress on Assignment #3 Intelligent Traffic Light Controller was going well. In summary:

- Traffic light lab module fully deployed in UTAR with a great demo using FPGA.

- Next steps are

- To enhance the lab content with more features for UTAR’s upcoming long-semester VLSI lab introduction in yr2021 (current lab is for short semester).

- Proliferate the lab module to UTAR Sg Long.

- Others

- To check with Intel expert on Synopsys TFM for Mixed-signal design and identify collaboration opportunity.

- UTAR internship requests for 10+ UTAR students.

Intel Handover of 20 Development Kits for FPGA

From left to right: Dr. Yeap Kim Hoe, Mr. Gan Chai Huat, Mr. Koay Boon Wooi, Dr. Loh Siu Hong, Dr. Yap Vooi Voon, Mr. Wong Chong Wai, Dr. Teh Eong Yap

Under the Intel® FPGA University Program, Intel Technology Sdn. Bhd, Penang donated 25 pieces of field-programmable gate array (FPGA) development boards to the Faculty of Engineering and Green Technology (FEGT) on 19 September 2018 at Kampar Campus. Present at the donation ceremony were FEGT Dean Assoc Prof Dr Yap Vooi Voon, and academics Assoc Prof Ir Dr Yeap Kim Ho and Ir Dr Loh Siu Hong. The delegates from Intel were Senior Manager of SoC team Wong Chong Wai, with his colleagues Gan Chai Huat, Koay Boon Wooi and Dr Teh Eong Yap.

The Intel® FPGA University Program is a programme that assists universities and colleges to develop and enhance knowledge in electronic engineering courses, such as computer systems design, digital logic design and embedded system design. Under this programme, Intel also offers donations of licenses for software and intellectual property (IP), and donations of FPGA hardware. Faculty and staff of universities and colleges can register as a member of the Intel FPGA University Program.

The development board that were donated are known as the DE1-SoC board, which is an educational tool intended for use in experiments on VLSI design and embedded systems. The system contains embedded processors, memory, audio, video device and some I/O peripherals.

FEGT expressed their gratitude to Intel for their kind donation, and for enabling the faculty to further develop and enhance students’ knowledge in electronic engineering courses. They believe the practical lessons using FPGA boards will provide students with the necessary practical skills demanded by the industries and increase their employability rate.

Currently, FPGA is used in several final year projects and postgraduate projects. It is also commonly used in undergraduate programmes. FEGT also expressed their hope for students to be able to acquire important skills in VLSI design and embedded systems and to be better prepared to be an integrated circuit design engineer, which is highly demanded in the electronics industry in Malaysia and globally.

|

| 2 |

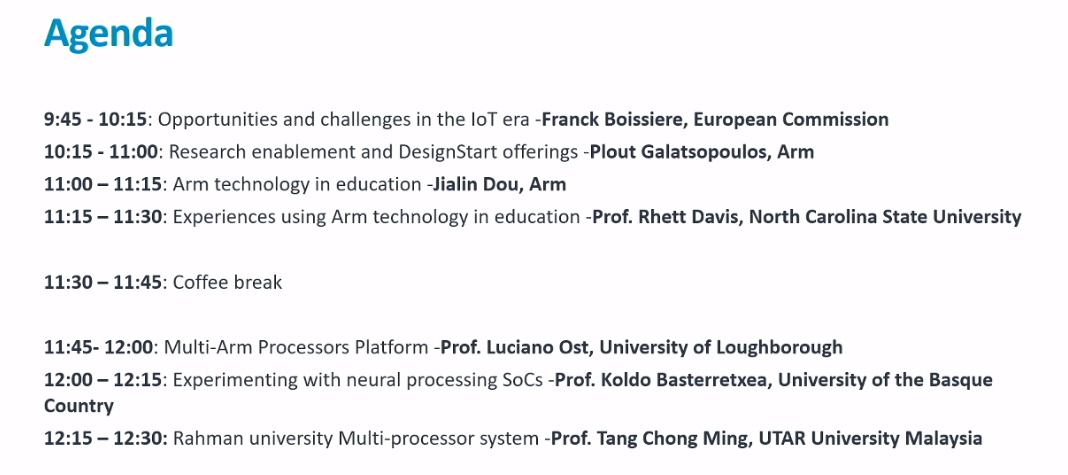

Subject: Arm Research Summit 2018 Speaker Invitation

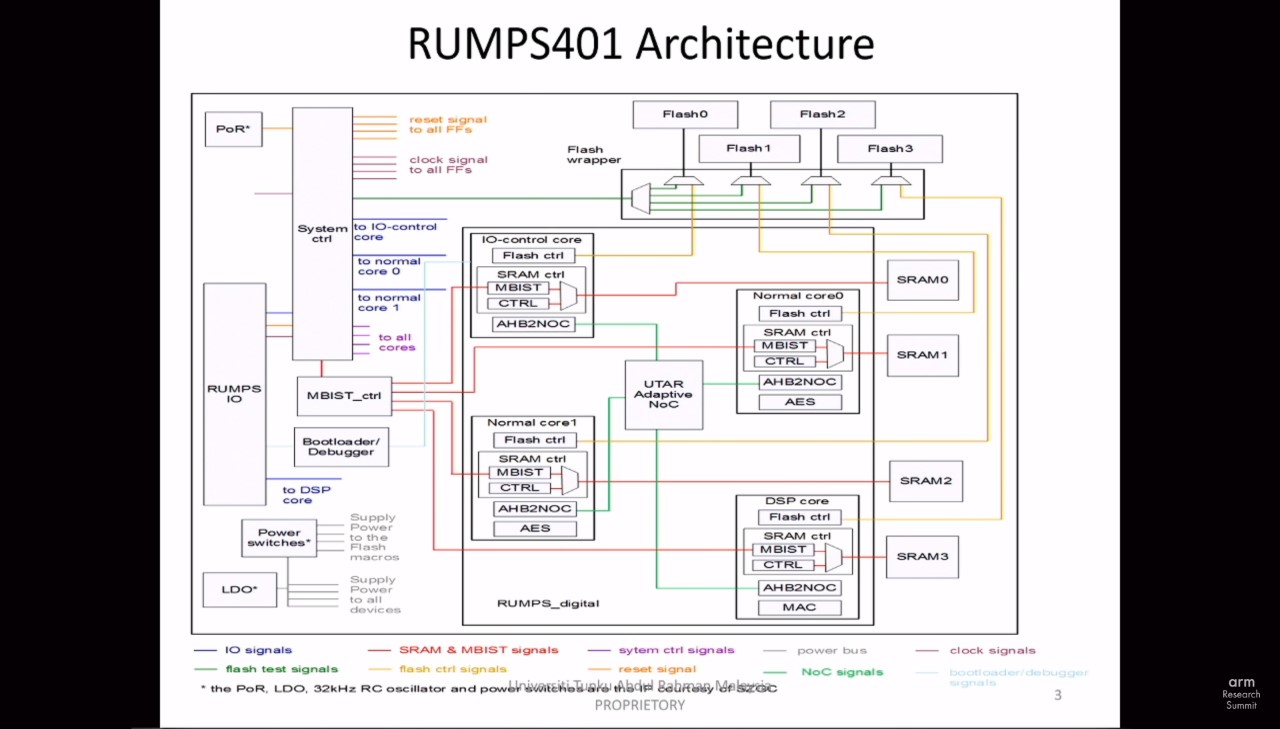

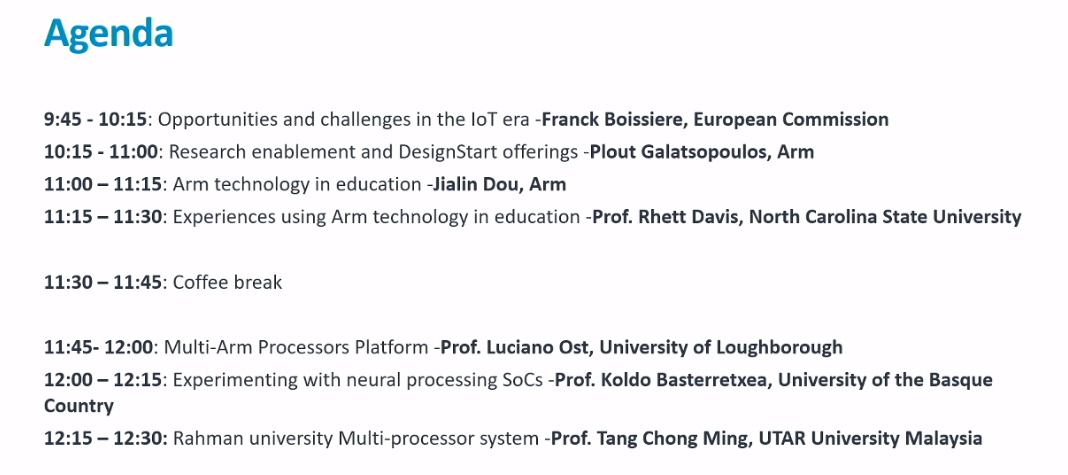

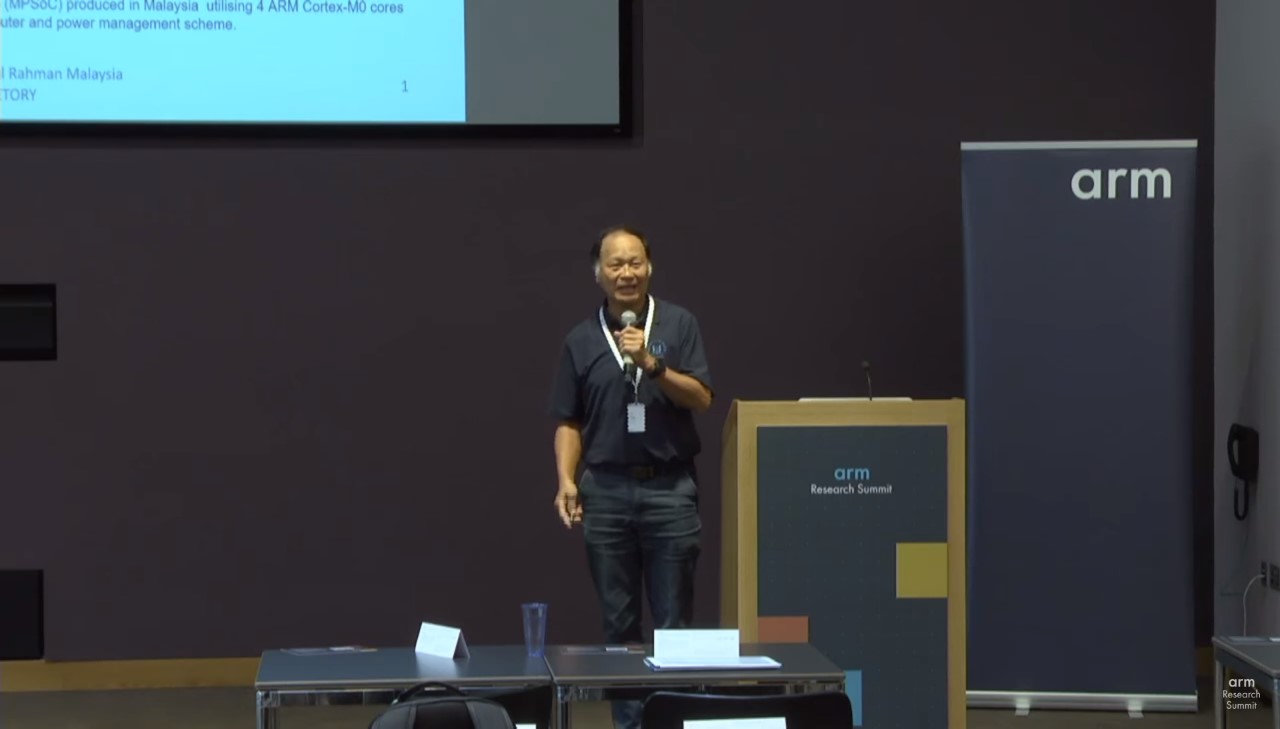

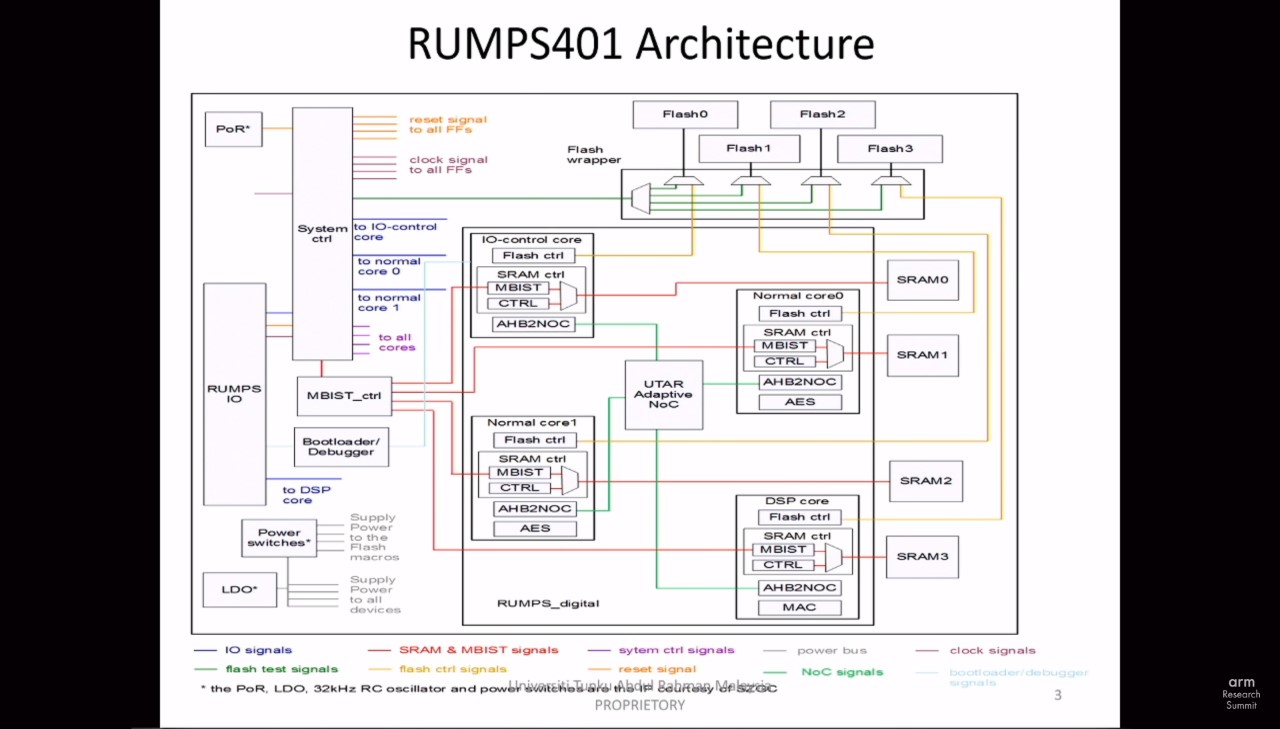

Prof. Tang Chong Ming was invited to attend Arm Research Summit and to present a 30 min invited talk on CVLSI project where CVLSI used the DesignStart Cortex-M0 processor and manufactured a chip RUMPS401 SoC using this technology. The third-annual ARM Research Summit – an academic summit to discuss future trends and disruptive technologies across all sectors of computing – took place in Cambridge, UK in September 2018.

Between 17-19 September 2018, researchers, academics and industry experts gathered at Robinson College in Cambridge, UK to discuss the latest trends, opportunities and challenges in computing research. The three days were packed with presentations, workshops, demos and networking, encouraging conversation and collaboration between attendees from around the world.

The Arm DesignStart program provides full access to industry proven processor technology (full RTL of Cortex-M0 and M3 integrated in a ready-to-use SoC) backed by the world’s largest software ecosystem. Revolving around the Arm DesignStart program, this workshop covered some ongoing initiatives at Arm to support education and research activities in Universities worldwide, including the Arm University Program and the Arm Research Enablement Program. Speakers include both Arm employees leading these initiatives as well academics who have already participated in them.

URL for video of Workshop presentation.

https://youtu.be/daSy03W74b8?list=PLr8iflX7VSAq0iOi7ha28JyVj4Bwtiat4 (Part 1)

https://youtu.be/GR22ElsudOs?list=PLr8iflX7VSAq0iOi7ha28JyVj4Bwtiat4 (Part 2)

https://youtu.be/daSy03W74b8 (Part 1)

https://youtu.be/GR22ElsudOs (Part 2)

Pictures (Screen captures) of Mr. Tang Chong Ming’s presentation in the workshop are illustrated below. To view the presentation, click on the URL given above.

Screen captures below are Q & A session at the end of the presentation.

The speaker for the CVLSI Research in the UTAR R & D Colloquium 2018 (1.0) was Dr. Khaw Mei Kum. The colloquium was held in Kampar on 21 April 2018.

Photo of venues

OVERALL PROGRAMME

| TIME | ACTIVITY | VENUE |

|---|

| 0830-0915 | Registration and Breakfast | LDK 1 FOYER |

| 0915-0930 | Opening remarks by VP(RDC), Prof Lee Sze Wei | |

| LDK 1 |

| 0930-0940 | Photo Session |

Parallel Session

1220 - 1320: Lunch & Networking Session, LDK 1 FOYER |

| 0940-1440 | Theme A

Healthcare & Wellness | LDK 1 |

Theme B

Disruptive/Advanced Technology | LDK 2 |

Theme C

Societal Impact of 4.0 IR | LDK 3 |

| 1440-1450 | Closing remarks by UTAR VP RDC, Prof Lee Sze Wei | LDK 1 |

| 1450-1500 | Networking Session & End of Colloquium | LDK 1 FOYER |

|